隨著倒裝芯片封裝在成本和性能上的不斷改進,加上鍵合金線價格的不斷攀升,從手機到游戲機芯片的各種應用領域里,倒裝芯片技術都變得更具競爭力。

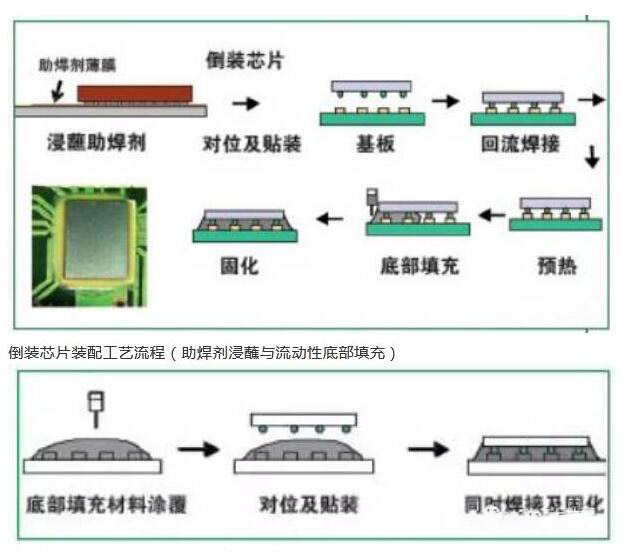

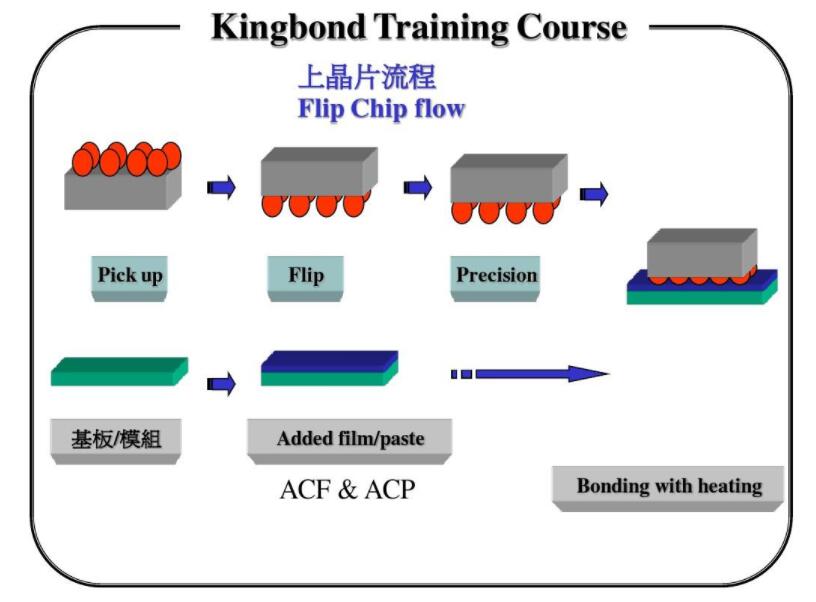

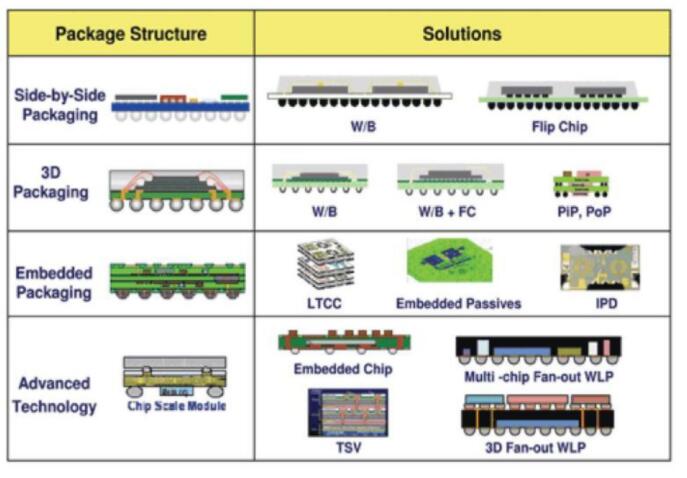

回首15年前,幾乎所有封裝采用的都是引線鍵合。如今倒裝芯片技術正在逐步取代引線鍵合的位置。倒裝芯片的基本概念就是拿來一顆芯片,在連接點位置放上導電的凸點,將該面翻轉,有源面直接與電路相連接。倒裝芯片避免了多余的封裝工藝,同時得到像縮小尺寸、可高頻運行、低寄生效應和高I/O密度的優點(圖1)。

在從手機和尋呼機到MP3播放器和數碼相機的所有熱門的消費類電子產品中,幾乎都能找到倒裝芯片封裝。在服務器中,近乎所有的邏輯模塊都采用倒裝芯片封裝。大部分ASIC、游戲機電路、圖形處理器、芯片組、現場可編程門陣列(FPGA)和數字信號處理器(DSP)也都已采用了倒裝芯片封裝(圖2)。

圖1. 像這個倒裝芯片BGA系統級封裝(SiP)的應用那樣,隨著金線鍵合成本的提升,對倒裝芯片的需求在不斷增加。

圖2. 為游戲機CPU設計的倒裝芯片BGA。

在過去幾年里金絲引線鍵合的成本不斷提高——這使得倒裝芯片變得更具吸引力。“如果看一下兩到三年前的成本,自然而然是倒裝芯片更高,” STATS ChipPAC(新加坡)負責倒裝芯片和新興產品的副總裁Raj Pendse這樣介紹。“通常來說倒裝芯片所用的封裝基板成本是引線鍵合襯底的兩到三倍,但金價的飆升卻超過了封裝基板的差價。在很寬泛的應用領域里,倒裝芯片已經成了更具成本效益的解決方案。過去兩種方法的成本平衡點是1000引腳。現在只要在200到700引腳范圍內,倒裝芯片就更劃算。”

倒裝芯片的歷史回顧

倒裝芯片技術的首次應用可以追溯到1964年。根據IBM封裝技術戰略部門的杰出工程師Peter Brofman介紹,那時他們已經在IBM S/360大型機中采用了混合固態邏輯技術(SLT)。這一技術主要是采用一些大節距的銅珠用作額外支撐,可以防止與無源器件之間的短路。“真正將倒裝芯片用在IC中始于1969年,但當時只有四邊引腳的方案,”他解釋說。“完全面陣列的金屬化陶瓷(MC)技術出現在70年代中期。在80年代早期,IBM已經可以完成11×11陣列、節距為250 μm的Pb-5Sn焊料球了。 ”

80年代末和90年代初,摩托羅拉從IBM獲得倒裝芯片的授權,開始尋找倒裝芯片陶瓷載體的替代物,開啟了對芯片到載體的下填充物以及低成本FR4有機材料的研究。IBM封裝工程經理Patrick OLeary指出,這些工作是與卡上加層的技術并行開發的,這一技術基于1990年的表面多層電路(SLC)工藝,到90年代中期,多芯片載體已經相當普遍。

“到1998年,大尺寸的微處理器開始采用芯片下填充料,并且轉向有機倒裝芯片加強載體,2000到2001年,35 mm、2-2-2載體基板的價格已經接近3美元,”O’Leary介紹說。“同引線鍵合相比,倒裝芯片仍‘有點貴’,但性價比已經很高,因此圖形處理器和游戲機處理器先后從倒裝芯片技術中獲益,到04、05年左右,已經完成了向有機倒裝芯片模塊的轉移。”

IBM已經將所有新的倒裝芯片單芯片模塊(SCM)轉向多層載體基板。O’Leary指出,處理器向倒裝芯片的重大轉移使得倒裝芯片模塊的年復合增長率(CAGR)比十年前提高了35%。“現在CAGR雖然低了一些,但仍然強勁,隨著金價的上揚,兩種方法的成本平衡點已經降到了200-700 I/O。在更低的引腳數下,整合器件制造商(IDM)將在他們的封裝方案中淘汰引線鍵合——很可能從32 nm節點開始。”

最近,倒裝芯片領域其他的里程碑還包括倒裝芯片的“凸點工藝”,或者說焊料沉積可選范圍的發展。90年代中期,像300 mm這樣的大尺寸晶圓驅使IBM和其他廠商從真空蒸發方法轉向電鍍方法。最近IBM和SUSS MicroTec(德國慕尼黑)共同開發并商業化了IBM的下一代無鉛半導體封裝技術,也就是可控塌陷芯片連接新工藝(C4NP),目前已進入量產。O’Leary指出,采用C4NP可以在前端就完成預先圖形化的焊料球,縮短了工藝流程的時間。可以預先檢查焊料凸點,并采用與晶圓級鍵合類似的技術,一步沉積在晶圓上。這種方法將焊料涂覆的簡便性(網版/絲印)和電鍍的窄節距能力結合在一起。“C4NP和電鍍方法都可以在產品中獲得150 μm的C4節距,從而滿足硅器件等比例縮減的要求,”O’Leary介紹說。 function ImgZoom(Id)//重新設置圖片大小 防止撐破表格 { var w=$(Id).width; var m=650; if(w

盡管當初IBM開發倒裝芯片技術是為了滿足大型計算機市場的要求,但倒裝芯片的應用范圍已經遠遠超出了計算機,Amkor(亞利桑那州,Chandler)負責倒裝芯片的高級主管Frederick Hamilton說。“倒裝芯片已經進入到計算機、無線通信、網絡、電信/數據、汽車和消費類電子(HDTV)市場,”他表示。“但PC仍然是半導體和倒裝芯片器件的最大單一用戶。”

有意思的是,倒裝芯片的平均現場壽命大約為15年——盡管部分產品的設計壽命是5年。Pendse還指出:“考慮到倒裝芯片的基本結構,很輕松地就可達到15年的現場壽命。”

關鍵的技術優勢

倒裝芯片的主要優勢包括可縮減和節省空間,此外還有互連通路更短且電感更低、高I/O密度、返工和自對準能力。對散熱管理來說,倒裝芯片的性能也很突出。

倒裝芯片可以采用面陣列互連,這意味著比四周排列封裝更高的I/O密度和更有效的電源供應。“如果需要的話,你可以將電源直接供應到芯片中間位置去。這有很大的優點。對RF和其他一些應用來說,倒裝芯片帶來的低寄生效應非常重要,”Pendse說。“另一個優點是因為芯片是與基板直接連接的,你就不需要扇出了——這與需要芯片到基板I/O扇出的引線鍵合不同。它意味著你可以獲得尺寸更小的封裝。”[page]

仍待解決的技術挑戰

隨著業界繼續降低技術節點,還有很多挑戰尚待解決。Hamilton認為,這包括需要改進封裝的電學/熱學性能、對尺寸縮減的持續需求、更窄的凸點節距,以及更短的上市時間,并且所有這些都需要在更低成本的前提下實現。

“業界還需要解決很多問題,像材料內的空隙、與低k材料兼容的凸點制作方法、低k材料與封裝的翹曲相關,而翹曲在薄層和無核多層基板中更加突出,”Hamilton表示。

當年業界從陶瓷基板轉換到有機基板時,也出現了很多嚴重的可靠性問題。Pendse說:“IBM聲稱,采用陶瓷基板和高鉛凸點的倒裝芯片封裝,在35年的運行時間中達到了零失效。”如果采用有機基板,由基板和芯片CTE失配引起的可靠性問題,以及有機基板自身的性能波動,使得現場失效的可能性大大提升。Pendse還補充:“新的鍵合結構、新的基板和隨之而來的質量波動,以及更高的CTE失配,都是需要解決的巨大挑戰。”

其他的挑戰還有采用倒裝芯片需要密度更高的基板,使得該技術比現行的引線鍵合技術更貴。Pendse介紹說,部分由于金價的上揚,部分由于互連結構和基板設計的不斷創新,目前價格因素的差異已經不那么顯著了。但隨著倒裝芯片在更寬的產品范圍得到接受,例如消費類電子產品,價格問題仍將是倒裝芯片技術的一個挑戰。

根據Brofman和O’Leary介紹,其他方面的挑戰還包括采用新型和改進的硅介電材料后,硅變得更加易碎,與此同時工業界還在關注超高互連密度的倒裝芯片陣列。芯片-封裝相互作用(CPI)——有限的可靠性、更高帶寬和更高密度——使得各方需要共同協作來解決這些問題。這也是為什么2008年在紐約州宣布建立一個封裝研發中心,以解決關鍵的倒裝芯片可靠性挑戰。一個例子是電遷移,由于電流密度過高引起導體中金屬原子的漸進流失,這將可能是窄節距C4面對的最大問題。

當前趨勢

Brofman和O’Leary都認為,倒裝芯片下一步的演進方向是芯片在插入層或者疊層芯片上的3-D集成。他們還指出,帶有穿透硅通孔(TSV)的芯片和晶圓減薄,以及超窄節距(50 μm)的新型Cu/Cu和銅柱互連都在開發中。此外為了滿足先進微處理器日益增長的功率密度要求,他們相信,疊層芯片方法將會在散熱管理上帶來很大挑戰。

Brofman還介紹說,封裝技術還持續地推動著材料科學與技術的發展。盡管他也認為碳納米管(CNT)互連還需要一些年的時間,但在近期,很可能采用納米材料作為芯片下填充料、導熱材料和多層復合基板的填充物。

Brofman還指出,在材料沉積領域也有一些新趨勢出現。“除了C4NP,在形成倒裝芯片互連時,還可以采用傳統BGA所使用的‘下投焊球’的方法。”

那么無鉛的趨勢呢?目前倒裝芯片模塊仍受到歐盟《限制使用有害物質條例》(RoHS)的豁免,并很可能會延續到2014年。“一般的觀點是如果使用無鉛材料制作凸點,將會遇到大量的可靠性問題,”Pendse介紹說。“即便硅進展到40 nm或更低節點,由于硅本身變得更脆,以及無鉛焊料本身更硬,這一問題將會更難解決。”工業界正在嘗試不同的凸點材料和方案,使互連變得更加柔順。

由于全世界范圍內電子產品的“綠色化”,長期來看,都會轉向無鉛的芯片互連,因此更多的倒裝芯片用戶將會采用無鉛模塊,這不僅僅是來自于法規的要求,也更是未來含鉛模塊能否進入市場的不確定性所驅使的,O’Leary介紹說。“多芯片模塊,特別是兩芯片模塊,已經比三年前更受歡迎。由于對電性能的追求,將會更多考慮更薄的基板核(0.4mm或更薄和/或無核有機倒裝芯片基板,”他說。“除了3-D集成在性價比上的提高外,像晶圓級芯片尺寸封裝所使用的晶圓級工藝技術也備受關注。”

Pendse預測,未來兩年內倒裝芯片領域的另一個趨勢是不斷滲透那些現在還較空白的領域——像音頻/視頻、錄像機、相機、MP3播放器、數字電視等這樣的消費類電子產品,可以受益于倒裝芯片出色的RF性能和可微縮能力。

用戶也在探索低成本倒裝芯片基板。“工業界一直在尋找可以有效布線以及芯片到基板互連的新設計方法,”Hamilton說。“目前正在研究的一種方法是用激光燒蝕將信號圖案寫到介電層,之后進行金屬化。”

在薄核基板方面,工業界將進入45nm及以下技術節點,芯片上晶體管的數目將會增加,開關速度也會提高,開關電壓將會降低,并且需要更短的信號通路降低寄生效應,Hamilton表示。“為了滿足這些需求,我們已經看到,目前標準的高性能倒裝芯片基板的核厚是800μm,業界已經開始向600μm或400μm前進。隨著核厚度的降低,我們面臨更多的基板和封裝翹曲的風險,其共面性將會挑戰當前工業界已經接受的標準。對更薄核以及無核基板的需求已經到來,為了戰勝這些風險和挑戰,封裝廠、基板供應商和組裝材料制造商已經開始共同協作努力。”

無核基板可以進一步提高倒裝芯片封裝的電學性能。無核基板中可以采用任一層作為電源或地,并可以在一層內完成所有的輸入端布線,在另一層完成所有的輸出端布線。這種基板還給芯片設計人員帶來極大的靈活性。

另一個趨勢是芯片頂部裸露、模塑的大尺寸高性能倒裝芯片。“模塑倒裝芯片方案的優勢在于可以支持薄核和無核方案,這樣就可以達到甚至超越工業界對共面性的要求,”Hamilton說。模塑封裝方案可以增進散熱性能,使芯片可以與外部的散熱部件通過一層熱界面材料直接接觸。這也是現有高性能單一或兩芯片封蓋方案的一個低成本替代方案,并提高了BGA焊料連接的可靠性。

最后但仍很重要、并值得討論的是銅焊柱。“采用焊料凸點倒裝芯片封裝方案進行器件微縮,同時會增加由于非常接近的相鄰凸點導致的嚴重的電遷移風險,”Hamilton解釋說。“這樣情況下,銅焊柱凸點可以降低這種風險,并可得到比當今的焊料凸點更窄的引腳間距。”其他優點還包括比焊料凸點更小的芯片/基板縫隙,并可降低阿爾法粒子。 function ImgZoom(Id)//重新設置圖片大小 防止撐破表格 { var w=$(Id).width; var m=650。

持續發展和最終的替代方案?

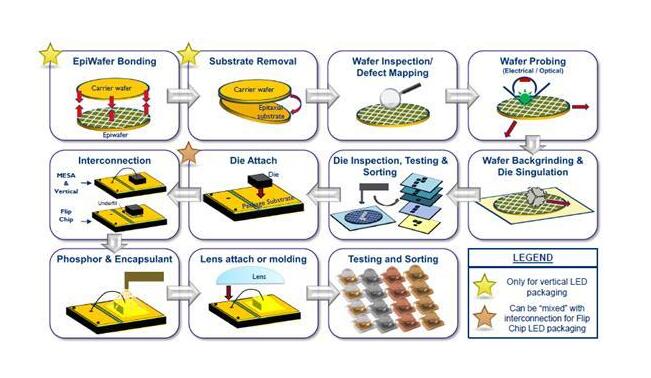

那么從現在開始倒裝芯片技術會向哪個方向變遷?Pendse介紹說,他期待未來的互連技術會有所不同。“起初,采用微凸點的TSV互連將會促進倒裝芯片的使用,它們與倒裝芯片不同,但是在同一陣營,”他說。“繼續前進的話,可能會出現更好的芯片鍵合技術。之后TSV本身可能會被看作是一種互連。倒裝芯片可能逐漸被其他方法所取代。”一種可能是將TSV作為互連(圖3),另一種可能是扇出型晶圓級封裝(FOWLP),也被稱為“先芯片封裝(chips-first packaging)”。

圖3. TSV可能最終會取代倒裝芯片。

Hamilton還指出,倒裝芯片也是下一代3-D IC架構的關鍵互連技術。“互連和封裝技術的壽命周期非常長,”他說。“到現在,即便倒裝芯片應用和技術已經發展得非常迅速了,還有大量的DIP(通孔互連)封裝存在。”

Brofman認為銅/銅鍵合或銅釘頭/凸點的潛力非常大,特別是在3-D集成領域,可能會取代倒裝芯片傳統的焊料沉積方法。“一些IDM也在開發小尺寸、低I/O、先芯片封裝技術,并且在低端倒裝芯片模塊方面顯示出良好的前景,”他補充說。

文章來自(www.4zj9t.cn)愛彼電路是專業高精密PCB電路板研發生產廠家,可批量生產4-46層pcb板,電路板,線路板,高頻板,高速板,HDI板,pcb線路板,高頻高速板,IC封裝載板,半導體測試板,多層線路板,hdi電路板,混壓電路板,高頻電路板,軟硬結合板等