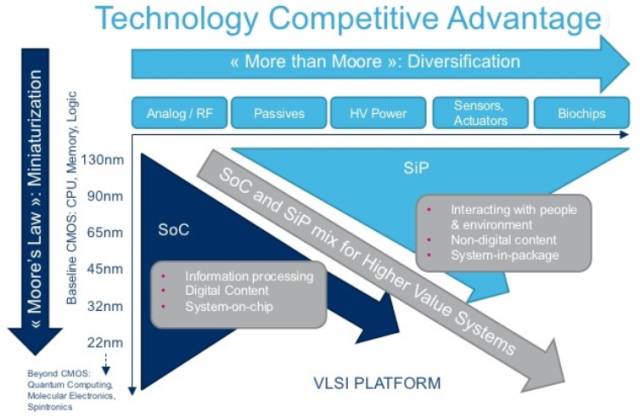

Mole定律作為電子制作產業鏈的金科玉律,一直矗立于科學技術進展的最前沿,給整個兒電子制作產業鏈指清楚十分清楚的趨勢,可以說厚澤萬物。但近些年,因為IC制作過程中運用的光刻技(Photolithography)相對于Mole定律顯得相對落后,IC業界給與厚望的EUV(Extreme UltraViolet)光刻設施也在緊鑼密鼓的開發中,技術成熟度尚達不到量產的水準,要得IC制導致本在晶圓節點(Wafer Node)不斷由大變小的事情狀況下,成本閃現指數提高;另一方面,2017年,水果A11/A10X、高通驍龍835、三星Exynos 8895、華為Kirin970和聯發科Helio X30蓄勢待發,晶圓節點已經進展到10nm量產的階段,已經十分靠近FinFET制程的物理極限5nm,也即即使EUV光刻設施可以量產運用,也沒有辦法變更Mole定律將要失去生命的發展方向。那接下來電子制作行業該何去何從?業界和教育界也給出了比Mole定律更為多元化的解答:more moore(深度Mole,IC制作角度的Mole定律)和more than moore(逾越Mole,IC封裝角度的Mole定律),見圖1:

圖 1 后Mole定律時期Roadmap

何謂深度Mole(more moore,IC制作角度的Mole定律),是延長下去CMOS(FinFET)的群體思考的線索,在部件結構、溝道材料、連署導線、高媒介金屬柵、架構系統、制作工藝等等方面施行創新開發,沿著Mole定律一路scaling(每兩到三年左右,結晶體管的數量翻倍),見圖2 Logic IC的roadmap:

圖 2 Wafer Node Roadmap

到現在為止深度Mole普通適合使用于數碼電路,如智強手機中的處置器(AP)和基帶芯片(Base Band),均歸屬SoC的范疇。面前我們也提到,因為FinFET的物理極限是5nm,那末進展到5nm后怎么樣接著呢?那就務必突破FinFET的結構和材料限止,研發和研討新的Transistor(switch)方式,如Tunneling FET(TFET)、Quantum Cellular Automata (QCA) 、SpinFET等,也即圖1中所說的的Beyond CMOS。

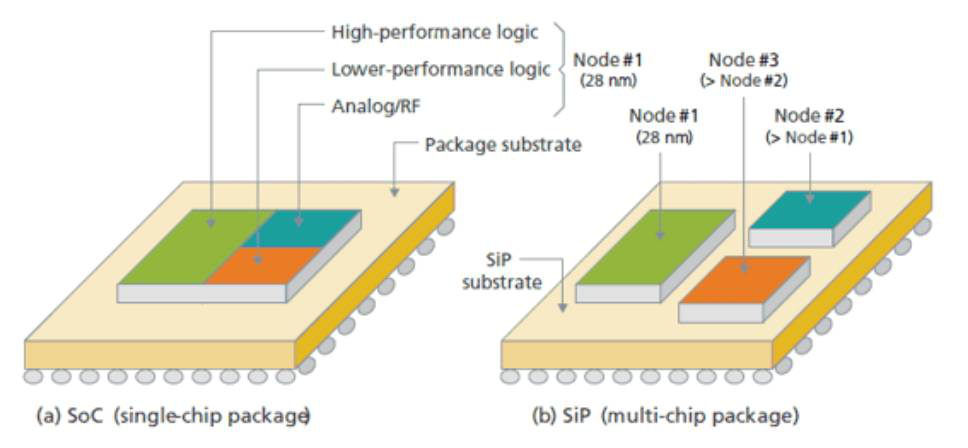

何謂逾越Mole(more than moore,IC封裝角度的Mole定律),主要偏重于功能的多樣化,是由應用需要驅動的。之前集成電路產業一直延長下去Mole定律而飛速進展,滿意了同一段時間許多人對計算、儲存的迫切地盼望與需要。但芯片系統性能的提高不再靠天真的暴力結晶體管scaling,而是更多地有賴電路預設以及系統算法優化,同時集成度的增長不盡然要靠暴力地把更多板塊放到同一塊芯片上,而是可以靠封裝技術來成功實現集成。摹擬/射頻/混合信號板塊等不必最先進工藝的板塊可以用較成熟且價格低廉的工藝成功實現(譬如為摹擬射頻工程師所喜聞樂見的65nm),而數碼板塊則可以由先進工藝成功實現,不一樣板塊可以用封裝技術集成在同一封裝中,而板塊間的通訊則運用高速接口。這種集成形式即異質集成(heterogeneous integration),是到現在為止在工業界和教育界都十分火的SiP,不惟可以降低成本,并且可以更加集成化,見圖3(b)。智強手機中的射頻前端板塊、WiFi板塊、藍牙板塊和NFC板塊等摹擬電路均適合使用于逾越Mole的情形。

回頭再看Mole定律的兩個方向,不過就是SoC和SiP的差別,一個是IC預設角度,一個是IC封裝角度,見圖3,也可是數碼電路與摹擬電路的差別。這么,再去了解SoC和SiP何其簡單。

圖 3 SoC與SiP

那我們再把眼看東西假想線從理論預先推測轉向實際應用,作為消費電子時期的弄潮兒水果企業天然是大家商議技術走向的焦點。隨著水果企業宣布iPhone 10周年的靠近,記念版iPhone的消息兒更是絡繹不絕,讓人目沒時間接,其最新技術走向更是值當大家剖析懸揣。

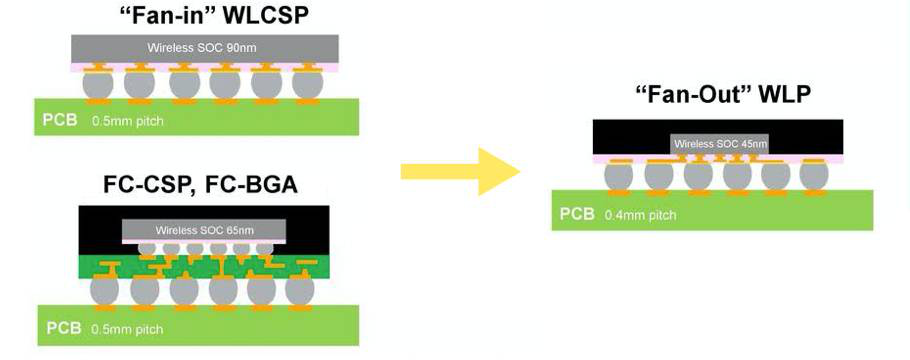

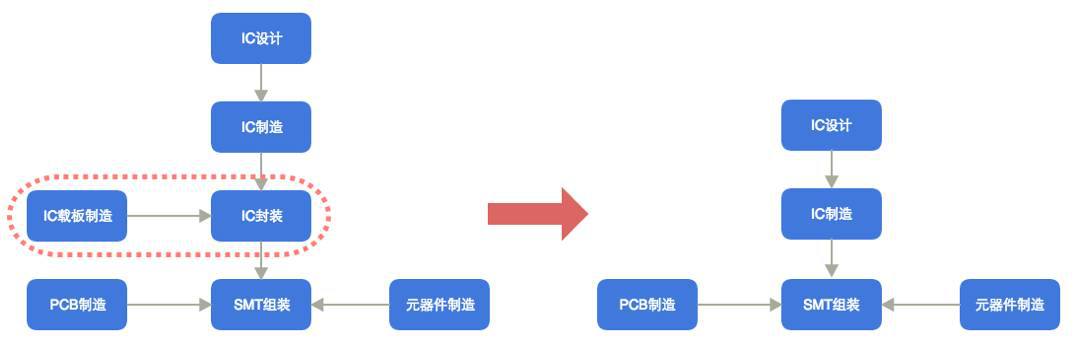

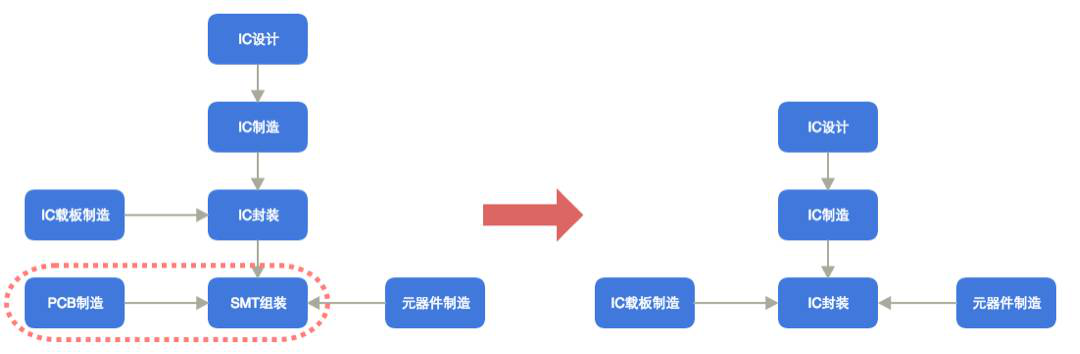

首先就是2016年九月iPhone 7的A10 Fusion第一次認為合適而使用TSMC 16nm 的InFoWLP封裝技術,絕對代替了過去的FCCSP的封裝技術,而說話時的這一年九月將要宣布的記念版iPhone A11將認為合適而使用TSMC 10nm的InFoWLP封裝技術,而與之對應的主板則會革命性地將載板的精密細致線路制作技術MSAP導入PCB行業,從新定義了電子制作產業鏈,因為原來的IC制作(TSMC)?IC封裝(ASE)+IC載板?SMT(Foxconn)+PCB制作流程改為IC制作(TSMC)? SMT(Foxconn)+PCB,也即把IC封裝融入IC制作,PCB直接接替IC載板。那我們不難發覺,這種是基于深度Mole因為AP 升班(16nm至10nm)而帶來的革命性變更。

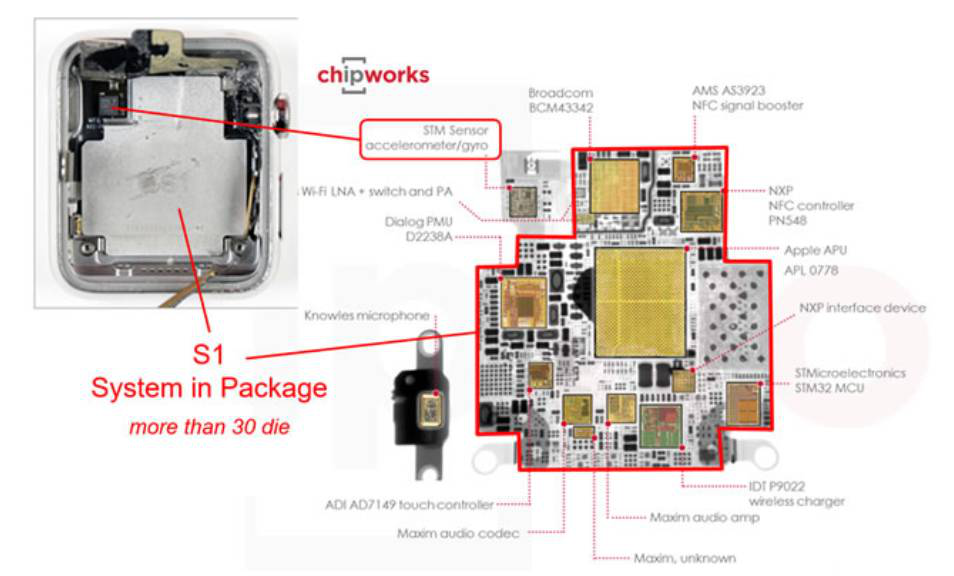

其次是水果Apple Watch的宣布,其最具獨特的風格的就是S1芯片(見圖4)的封裝技術,即SiP封裝技術(System in Package),不惟把AP應用法置器(已經集成了SRAM內存)、NAND閃存、各種傳感器、特別用場芯片、IO及功耗管理IC封裝到達一塊兒,并且還把其它不主動原件均集成在一塊載板上,在這處其主板客串了兩個角色:IC載板和PCB主板,其整個兒電子制作產業鏈也由傳統的IC制作(TSMC)IC封裝(ASE)+IC載板SMT(Foxconn)+PCB縮減為IC制作(TSMC)IC封裝(ASE)+IC載板,也即把SMT流程所有整合入IC封裝,并認為合適而使用IC載板接替PCB主板。從這個時候起我們也不不好看出,這種就是基于逾越Mole因為封裝技術的鼎新而帶來的革命性整合。

圖 4 Apple Watch S1

從以上水果企業最新的技術應用剖析,我們可以看出,水果、臺積電、日子色和富士康四親昆季作別代表著IC預設、IC制作、IC封裝和SMT四個領域正忠實地沿著深度Mole和逾越Mole的路線前行,引領者整個兒電子制作行業的進展與變法,同時也潛移默化地影響著PCB制作者和IC載板制作者。作為PCB制作的在業者,更需求擦亮眼球,做到envision it,enable it,只有這么能力永葆。下邊我將從IC封裝和IC載板技術方面談起,更周密地紹介Fan-Out WLP、SLP和SiP,為PCB產業后續進展和遠景計劃供給提議。

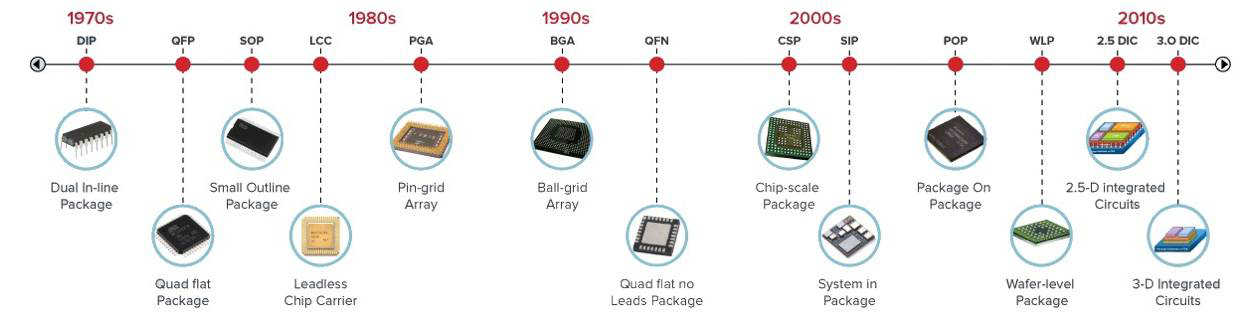

電子制作產業鏈里面含有前端的高端電子產業鏈(IC預設、IC制作和IC封裝)和后端的SMT貼件及組裝,所以IC封裝技術歸屬高端電子制作領域非常關緊的一環,其技術進展發展方向一樣受Mole定律的影響,當然現階段一樣受困于Mole定律的限制性影響。隨著高速數值傳道輸送的需要及無線技術的飛速進展,沿著深度Mole的方向,芯片尺寸不斷由大變小,I/O數不斷增加,傳統的IC封裝正漸漸由Lead frame、Wire Bonding轉向Flip Chip,見圖5,因此防止互聯通道過長對數值傳道輸送通道導致的信號虧損;當IC制作遭受好些個限止因素,Mole定律漸漸趨緩時,許多人只得開辟逾越Mole的進展道路,從起初的單個IC對應單個載板的封裝走向多個IC對應單個載板的SiP封裝(2D、2.5D、3D封裝)。

圖 5 封裝技術進展Timeline

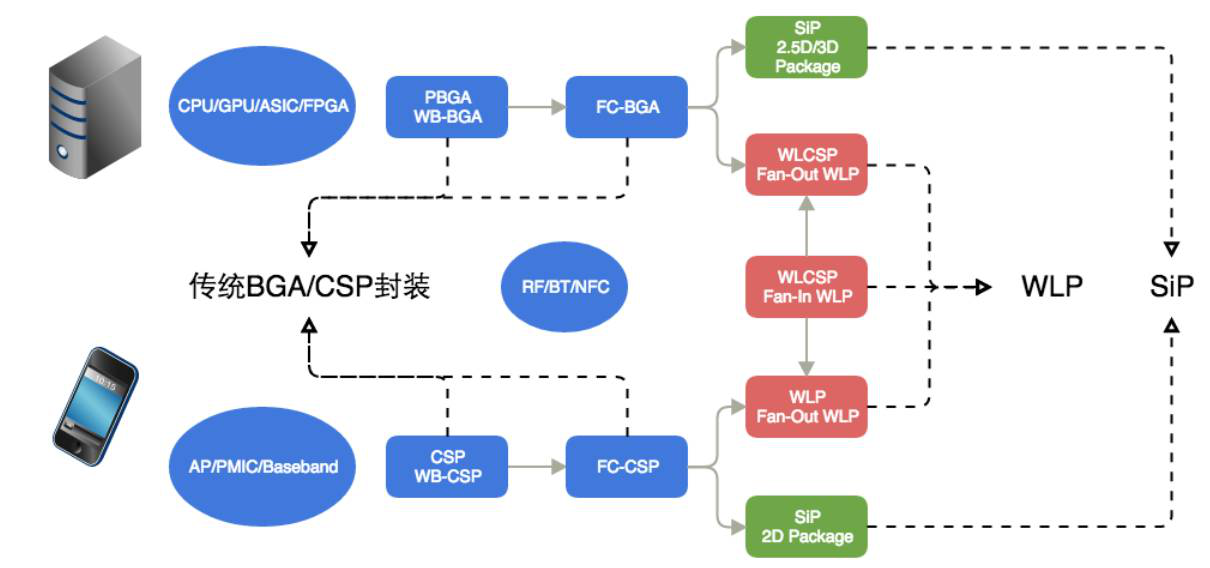

為了更周密的理解IC封裝技術及其所里面含有的IC載板技術,我們需求將視角由Mole定律轉向IC實際應用。縱觀ICT時期,電子制作技術的主要驅動出處于兩個方面:第1,以智強手機為中心的消費電子,第二,以大數值云計算為中心的高性能計算機,不一樣的應用對應不一樣的IC封裝和IC載板,見圖6:

圖 6 IC封裝應用及衍變發展方向

從圖中我們也可看出,主流IC封裝主要涵蓋3個大類:傳統BGA/CSP封裝、WLP封裝和SiP,所以我將從以下三大類封裝論述IC載板、SLP、FoWLP及SiP的差別。

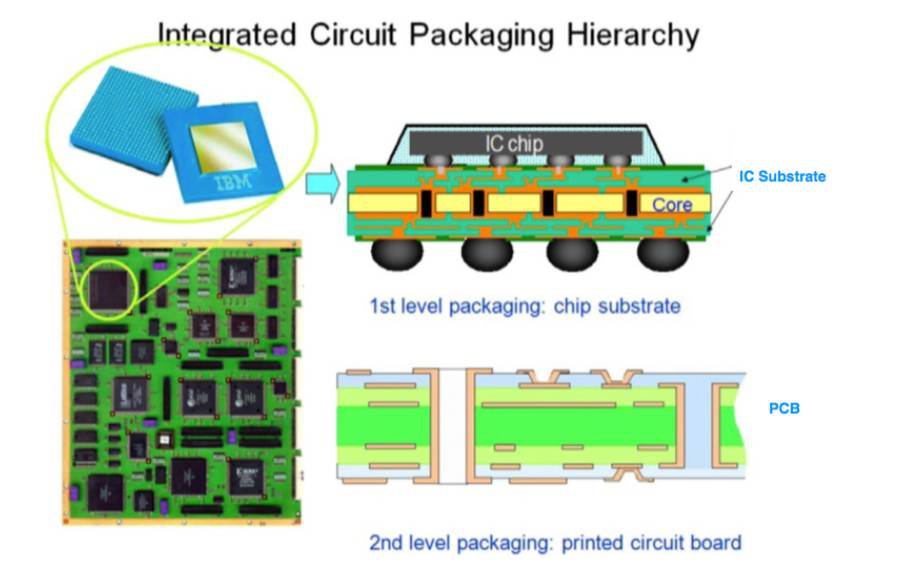

意義廣泛上的封裝涵蓋兩局部,一級封裝IC載板和二級封裝PCB(SMT),我們所說傳統的BGA/CSP封裝即為一級封裝,即把裸芯片經過wire bonding或是flip chip的形式與IC載板施行互聯而后塑封即完成了封裝,見圖7:

圖 7 封裝等級

因為一級封裝時,IC裸芯片與IC載板互聯時普通認為合適而使用高熔點的鉛錫合金,熔點在300度以上,凌駕二級封裝SMT燒焊溫度260度40多度,所以對IC載板的耐熱性及CTE(α2 X、Y CTE 5-7ppm/℃)要求極高,這就是IC載板運用的板材務必為高剛性低CTE 變態板材或FR5板材的端由,也是IC載板差別于PCB(α2 X、Y CTE 15ppm/℃)的第1大獨特的地方。

2.1.1 IC載板的類型

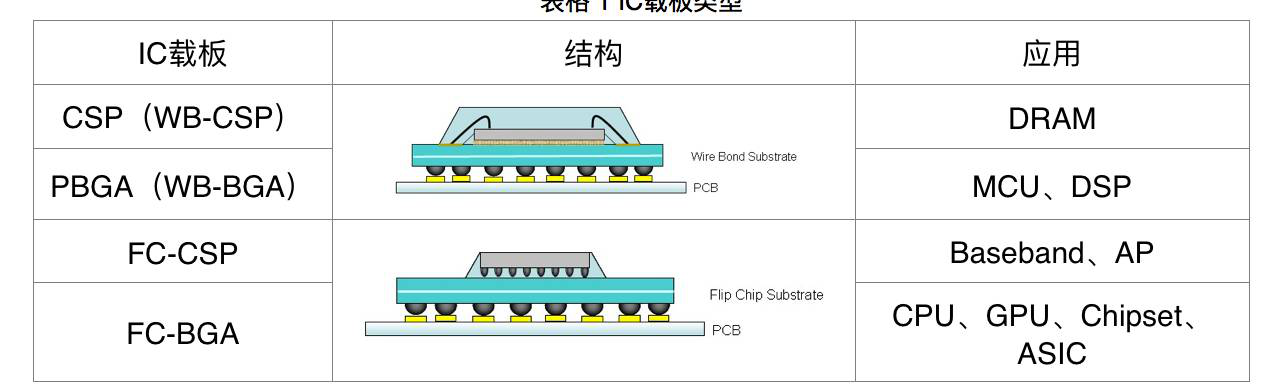

應用于智強手機的消費電子IC封裝主要思索問題便攜性、低成本等因素,普通認為合適而使用CSP封裝,封裝尺寸較小,而應用于高性能計算機的IC封裝,主要思索問題性能,普通認為合適而使用較為大型的、I/O數太多的BGA封裝。到現在為止主流的IC載板類型見表格1:

2.1.2 IC載板精密細致線路加工技術

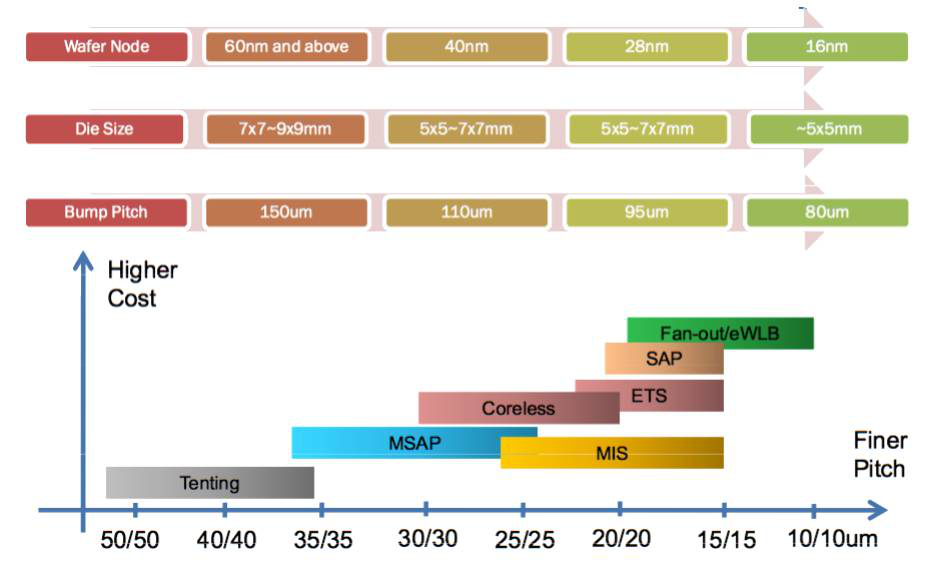

隨著IC預設節點的不斷由大變小,IC尺寸也不斷由大變小,因此造成了IC封裝時的Bump pitch也漸漸由大變小,從下圖可以看出,當IC Bump Pitch在150um以下時,常理的tenting酸蝕流程加工已經沒有辦法滿意IC載板的精密細致線路加工要求,務必認為合適而使用MSAP、SAP或是大致相似流程。這是IC載板差別于PCB的第二大獨特的地方。

圖 8 IC載板精密細致線路加工技術

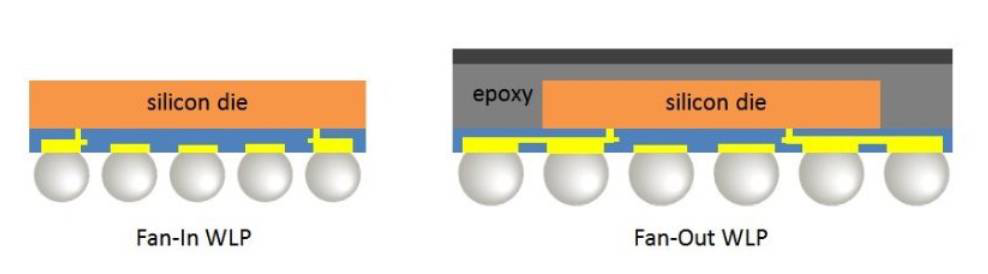

晶圓級封裝(WLP,Wafer Level Package) 的普通定義為直接在晶圓向上行大部分數或是所有的封裝測試手續,在這以后再施行割切(singulation)制成單顆組件。而從新分配(redistribution layer, RDL)與凸塊(bump)技術為其I/O布線的普通挑選,因此脫離了對IC載板的倚賴,封裝成本大大減低。WLP封裝具備較小封裝尺寸(CSP),但同時,因為凸塊所有位于芯片下方,I/O數遭受大大限止,所以,WLP封裝普通又叫作為WLCSP或是Fan-In WLP,到現在為止多用于低腳數消費性IC的封裝應用。

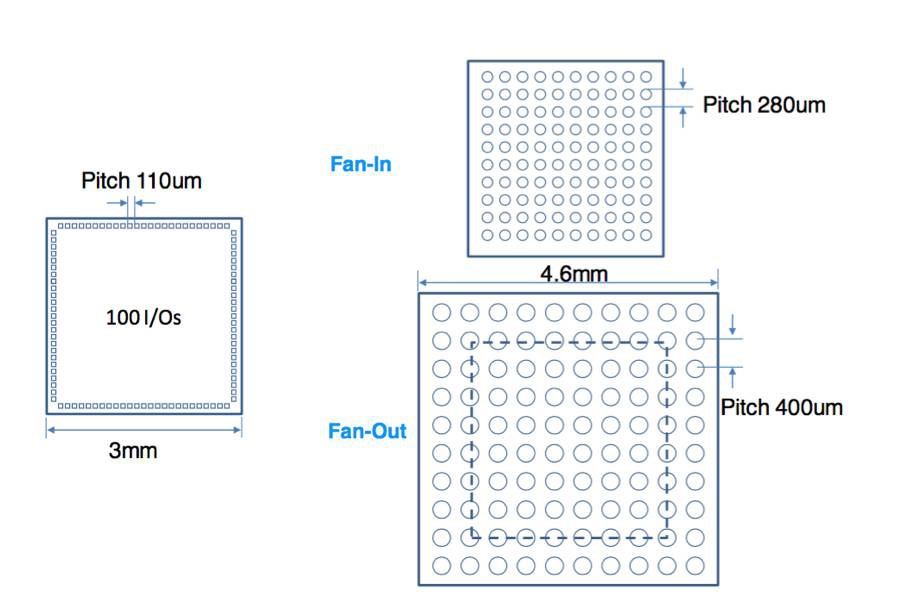

隨同IC芯片I/O數量增加,對錫球間距(Ball Pitch)的要求更加嚴明, 到現在為止Ball Pitch已經進展至0.35mm,假如連續不斷減低,將會導致下游PCB制導致本大大增加,于是Fan-Out WLP應運而生,見圖9:所說的Fan-Out,即I/O bump可以經過RDL層擴展至IC芯片周邊,在滿意I/O倍增大的前提下又不至于使Ball Pitch過于由大變小因此影響PCB加工,見圖10。

圖 9 Fan-In and Fan-Out

圖 10 Fan-Out WLP

當然,Fan-Out WLP除開滿意不斷增加的I/O數的需要外,最大的獨特的地方就是其認為合適而使用RDL層布線接替了傳統IC封裝所需的IC載板,因此大大減低了群體封裝厚度,這一點兒莫大地適合了消費類電子特別是智強手機對厚度的極度要求過嚴。基于此點,傳統的FC-CSP和FC-BGA封裝也漸漸向Fan-Out WLP過渡,當然也可了解為Fan-Out WLP是Fan-In WLP和FC載板封裝的技術合成一體,見圖11。可見Fan-Out WLP進展前面的景物非同普通。

圖 11 Fan-Out WLP進展發展方向

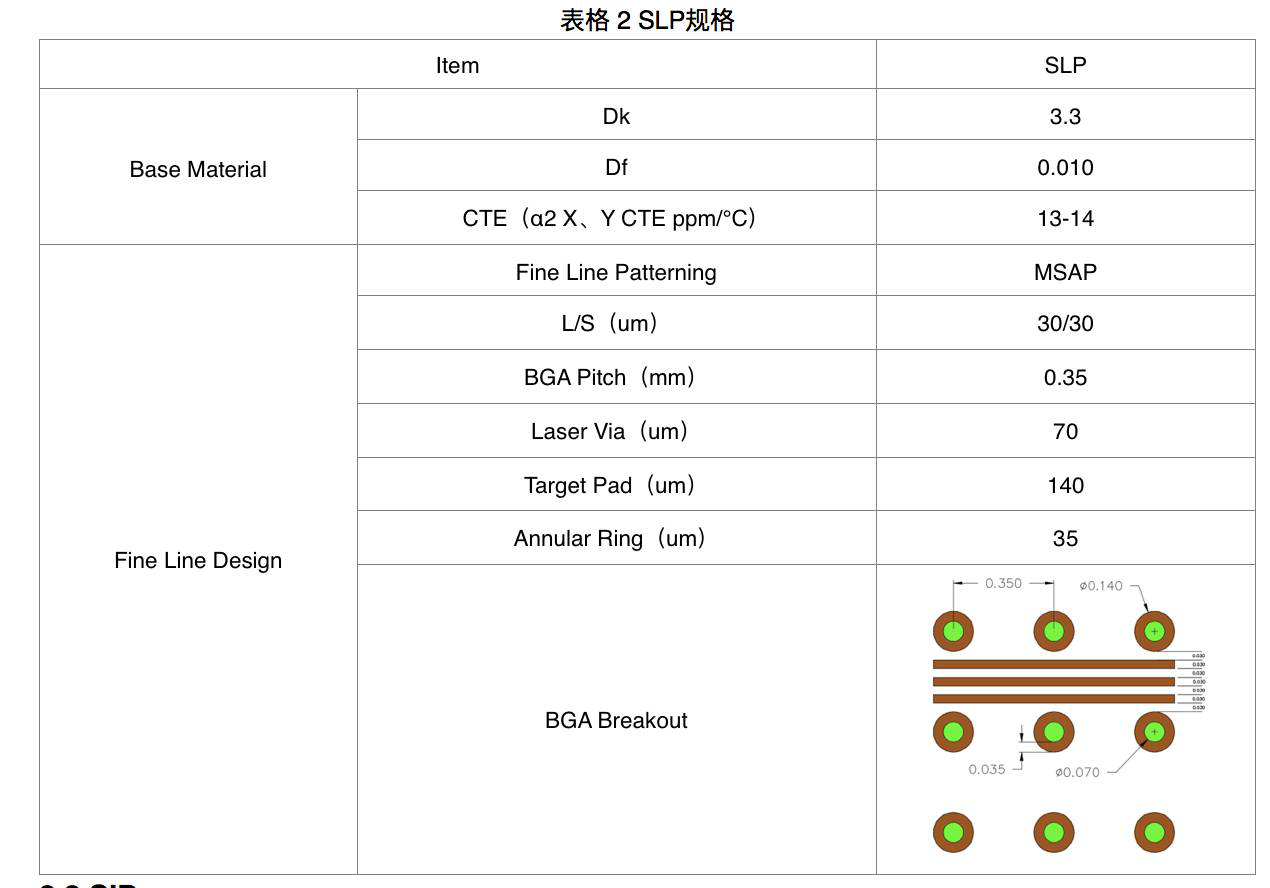

隨同Fan-Out WLP技術興起,相組成一套的PCB因為運用了IC載板的精密細致線路加工技術MSAP,其加工困難程度卻又遠高于常理HDI。額外,因為IC芯片認為合適而使用Fan-Out WLP后,已經不再是裸芯片(IC載板是裸芯片封裝,這也是IC載板差別于PCB的第三大獨特的地方),所以與之組成一套的PCB并不可以稱為載板,依據到現在為止水果電子產業鏈的業內之人所述,把認為合適而使用Fan-Out WLP封裝和認為合適而使用MSAP工藝加工的PCB稱為類載板PCB(SLP,Substrate-like PCB)。Apple 2016年宣布的iPhone7的A10 Fusion已經認為合適而使用TSMC InFoWLP工藝,但PCB還是認為合適而使用酸蝕流程,據獲悉,2017的A11芯片也將延長下去TSMC InFoWLP工藝,況且已經確認PCB認為合適而使用MSAP流程,所以,類載板PCB的定義和技術指標也變得更加具體,見表格2:

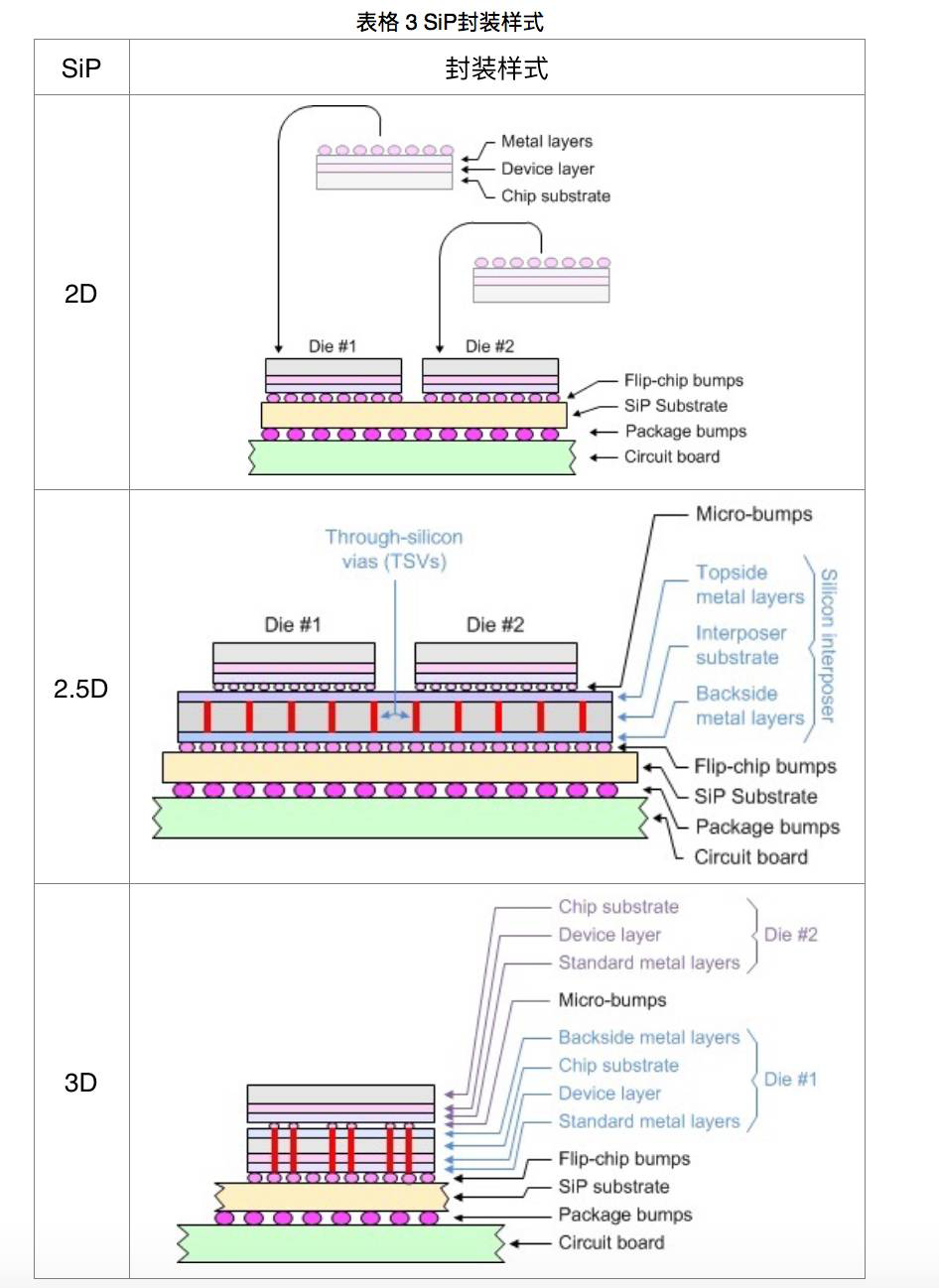

依據國際半導體路線團體(ITRS)的定義,SiP是從封裝的角度動身,對不一樣芯片施行并排或疊加的封裝形式,將多個具備不一樣功能的有源電子元件與可選無源部件,以及諸如MEMS還是光學部件等其它部件優先組裝到一塊兒,成功實現一定功能的單個標準封裝件,形成一個系統還是子系統。

SiP可相當于一系統載板的有關功能芯片、電路的全體,而根據不一樣的功能芯片施行系統封裝,可以采簡單的Side by Side的MCM(Multi-chip Module)技術(2D Package),也可利用相對更復雜的多芯片封裝MCP(Multi-chip Package)技術、芯片堆疊(Stack Die)等不一樣困難程度與制造形式施行系統組構(2.5D和3D Package)。也就是說,在純一個封裝體內不但可使用多個芯片施行系統功能構造,甚至于還可將里面含有前述不一樣類型部件、不主動元件、電路芯片、功能模組封裝施行堆疊,透過內里串線或是更復雜的3D IC技術整合, 構建成更為復雜的、完整的SiP系統功能。常見的SiP封裝式樣見表格3:

從上表可以看出,SiP 載結實際上就是IC載板的一種,其技術和規格和傳統BGA/CSP封裝相兒同。面前我們提到的Apple Watch S1芯片認為合適而使用SiP封裝,實際上是一種比較特別的IC載板,既可稱作IC載板也可稱作PCB主板。

在后Mole定律時期,正如前言所述,整個兒電子產業鏈正沿著深度Mole和逾越Mole兩條道路前行,也潛移默化的整合著整個兒電子制作產業鏈的布局。

隨著晶圓廠在先進制程上的發展,不斷滿意Mole定律的要求,每一顆晶圓的尺寸在不斷由大變小。不過,同制作技術不一樣,后道封測并不絕對遵照Mole定律的進展,換句話說,直接在晶圓上的植球尺寸,不會滿意同比例由大變小的技術演變進化。對于封測廠商來說,隨著I/O口的增多和晶圓尺寸的由大變小,怎么樣再滿意封裝管腳的引出是一大挑戰。而對于晶圓廠來說這確是一個機會。說話時的這一年九月將要宣布的記念版iPhone A11將認為合適而使用TSMC 10nm的InFoWLP封裝技術,而與之對應的主板則會革命性地將載板的精密細致線路制作技術MSAP導入PCB行業,從新定義了電子制作產業鏈,因為原來的IC制作(TSMC)?IC封裝(ASE)+IC載板?SMT(Foxconn)+PCB的制作流程改為IC制作(TSMC)? SMT(Foxconn)+PCB,也即把IC封裝融入IC制作,PCB直接接替IC載板。見圖12:

圖 12 電子制作產業鏈整合發展方向1

這么,以前一度由封裝廠主導和掌控的IC封裝市場漸漸被IC制作公司晶圓廠吞食。各大晶圓廠如三星和Intel也在積極布局大致相似于InFoWLP的高端封裝技術,漸漸強力奪原有IC封裝廠的市場訂單。

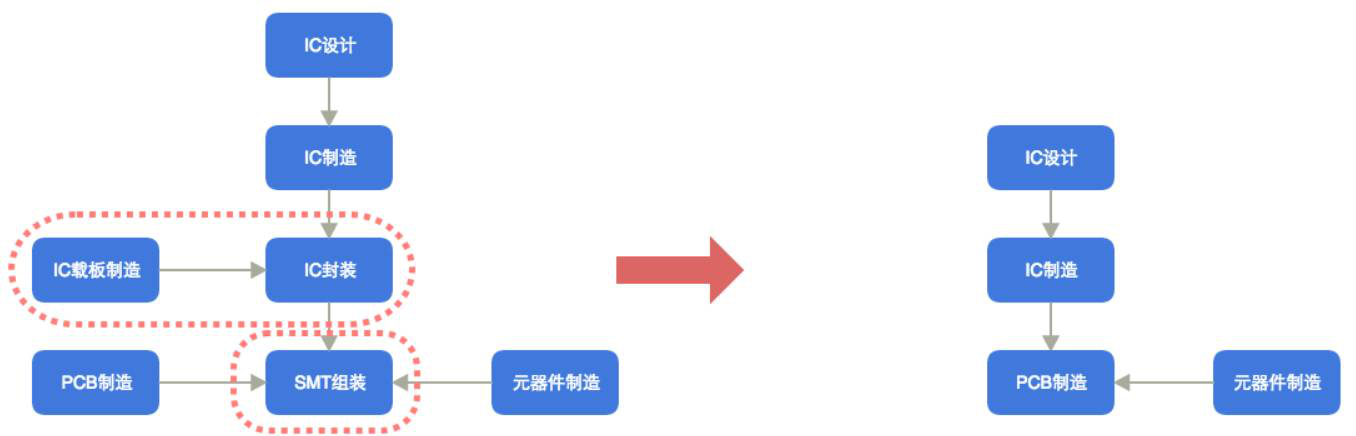

Apple Watch S1芯片的SiP封裝,其整個兒電子制作產業鏈也由傳統的IC制作(TSMC)?IC封裝(ASE)+IC載板?SMT(Foxconn)+PCB縮減為IC制作(TSMC)?IC封裝(ASE)+IC載板,也即把SMT流程所有整合入IC封裝,見圖13:

圖 13 電子制作產業鏈整合發展方向2

這么,封裝廠需求供給:從芯片封裝到系統集成的群體解決方案;具有系統預設和測試有經驗;除開傳統芯片封裝以外,EMI防備保護,3D/鑲嵌式封裝結構,鑲嵌式接收天線等高集成度方案的know how,都將由封裝廠來掌握。進一步而言,封裝廠將從天真地為某一家IC預設公司供給芯片封裝方案,轉成為為下游的整機商供給完整的系統解決方案。

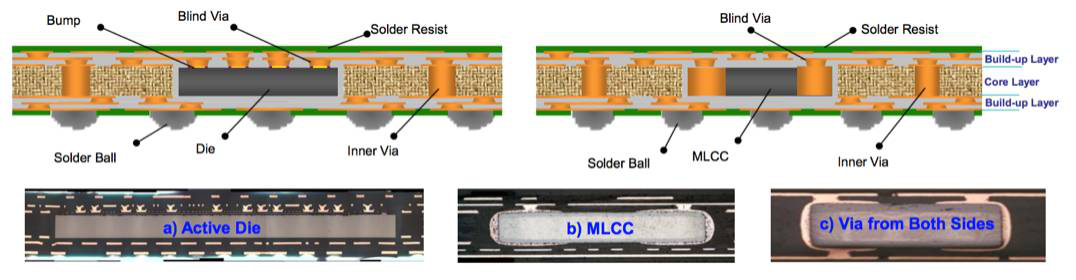

隨著SiP封裝技術的不斷進展,越來越多的元部件被埋入IC載板,原來的埋入不主動元件已經司馬見慣,埋入主動元件如IC等正風起云涌,以進一步提高集成度,見圖14。

圖 14 PLP

同時,隨著IC制作領域的光刻對位技術的逐層提高,晶圓尺寸漸漸由200mm、300mm向450mm、500mm的大拼板方向提高,所以越來越多的科學技術辦公者覺得,假如直接將IC等主動元件和其它不主動元件在PCB 大拼板加工過程中直接埋入,那將大大縮減整個兒電子制作產業鏈,見圖15。

圖 15 電子制作產業鏈整合發展方向3

到現在為止已有多個電子行業在業單位研發出相應的PLP產品,有PCB廠家AT&S的ECP(Embedded Components Packaging),有IC載板廠家ASE的a-EASI(advanced-Embedded Assembly Solution Integration),也有IC載板廠家Kinsus的EAS(Embedded Actives Substrate)。