高速電路板設計技術阻抗匹配是指負載阻抗與激勵源內部阻抗相互適應,獲得最大功率輸出的一種工作狀態。為了防止高速PCB布線時的信號反射,要求電路的阻抗為50Ω。這是一個近似數字。一般規定同軸電纜的基帶為50Ω,頻帶為75Ω,雙絞線為100Ω。它只是一個整數,為了匹配方便。

根據具體電路分析,采用并聯交流終端,電阻電容網絡作為終端阻抗。端接電阻R必須小于或等于傳輸線阻抗Z0,電容C必須大于100pF。推薦使用0.1UF多層陶瓷電容。電容具有阻低頻通高頻的作用,所以電阻R不是驅動源的直流負載,所以這種端接方式沒有任何直流功耗。

串擾是指信號在傳輸線上傳播時,由于電磁耦合到相鄰傳輸線上而引起的不希望有的電壓噪聲干擾。耦合分為電容耦合和電感耦合。過大的串擾可能會導致電路誤觸發,導致系統無法正常工作。根據串擾的一些特點,可以總結出幾種降低串擾的方法:

1、增加線距,減少平行長度,必要時采用點動法接線。

2、當高速信號線滿足條件時,增加端接匹配可以減少或消除反射,從而減少串擾。

3、對于微帶傳輸線和帶狀傳輸線,將走線高度限制在地平面范圍內可以顯著降低串擾。

4、在布線空間允許的情況下,在串擾比較嚴重的兩根線之間插一根地線,可以起到隔離的作用,從而減少串擾。傳統PCB設計由于缺乏高速分析和仿真指導,信號質量無法保證,大部分問題要到制版測試才能發現。這大大降低了設計效率,增加了成本,在激烈的市場競爭中顯然處于劣勢。

因此,對于高速PCB設計,業內人士提出了一種全新的設計思路,成為一種“自頂向下”的設計方法。經過各種策略分析和優化,大部分可能出現的問題都被規避了,節省了很多。確保滿足項目預算、生產高質量印制板并避免繁瑣且代價高昂的測試錯誤的時間。使用差分線傳輸數字信號是控制高速數字電路中破壞信號完整性因素的有效措施。

印刷電路板上的差分線相當于工作在準TEM模式下的差分微波集成傳輸線對。其中,位于PCB頂部或底部的差分線相當于耦合微帶線,位于多層PCB內層的差分線相當于寬邊耦合帶線。

數字信號以奇模傳輸方式在差分線上傳輸,即正負信號的相位差為180,噪聲以共模方式耦合在一對差分線上,接收器中的正負兩個通道的電壓或電流相減,從而得到消除共模噪聲的信號。差分對的低電壓幅值或電流驅動輸出,實現了高速集成和低功耗的要求。

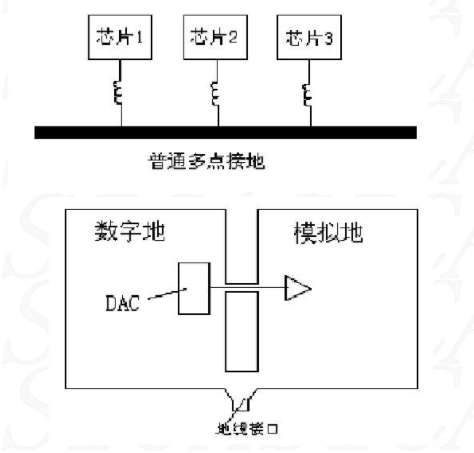

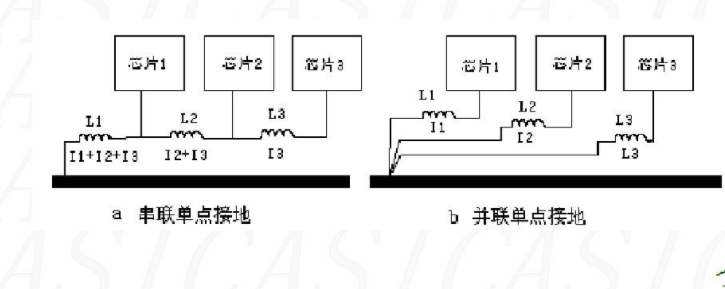

三種接地方式:

1、單點接地:適用于低頻電路,優點是保證接地回路互不干擾。

2、浮地:可以將電路板地與其他地隔離,減少干擾。常用于工業控制和PLC。

3、多點接地:高速電路使用,優點是接地回路阻抗最小。