假如高速PCB預設能夠像連署原理圖節(jié)點那樣子簡單,以及像在計算機顯露器上所看見的那樣子優(yōu)美的話,那將是一件多么美事。不過,錯非預設師初入PCB預設,還是是極端的幸運,實際的PCB預設一般不像它們所投身的電路預設那樣子輕松。在預設最后能夠正常辦公、有人對性能作出肯定之前,PCB預設師都面對著很多新的挑戰(zhàn)。這正是到現(xiàn)在為止高速PCB預設的目前的狀況--預設規(guī)則和預設指南不斷進展,假如幸運的話,他們會形成一個成功的解決方案。

絕大部分數(shù)PCB是洞曉PCB部件的辦公原理和互相影響以及構成電路板輸入和輸出的各種數(shù)值傳道輸送標準的原理圖預設師與有可能曉得一點兒甚至于有可能一點兒也不曉得將小小的原理圖串線改換成印刷電路銅線后將會發(fā)生之類專業(yè)版圖預設師互相合作的成果。一般,對最后電路板的勝敗負責的是原理圖預設師。不過,原理圖預設師對優(yōu)秀的版圖技術知道越多,防止顯露出來重大問題的機緣就越多。

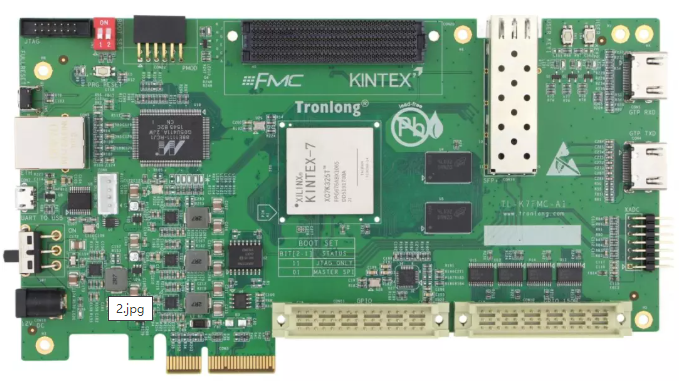

假如預設中包括高疏密程度的FPGA,很有可能會有很多挑戰(zhàn)安擺放置在專心預設的原理圖面前。涵蓋數(shù)以百計的輸入和輸出口數(shù)目,超過500MHz(某些預設中有可能更高)的辦公頻率,以及小至半毫米的焊球間距等,這些個都將造成預設單元之間萌生不應有的互相影響。

并發(fā)開關噪聲

第1個挑戰(zhàn)很有可能就是所說的的并發(fā)開關噪聲(SSN)或并發(fā)開關輸出(SSO)。數(shù)量多的高頻數(shù)值流將在數(shù)值線上萌生振鈴和串擾什么的的問題,而電源和地最簡單的面上也會顯露出來影響整個兒電路板性能的地線反彈和電源噪聲問題。

為理解決高速數(shù)值線上的振鈴和串擾,改用差分信號是美好的第1步。因為差分對上的一條線是借鑒(Sink)端,另一條供給源電流,因為這個能除根感應影響。利用差分對傳道輸送數(shù)值時,因為電流維持在部分,因為這個有助于減小回返途徑中的感應電小產(chǎn)生的“反彈”噪聲。對于高達數(shù)百MHz甚至于數(shù)GHz的射頻,信號理論表明,在阻抗般配時可以傳遞最大信號功率。而傳道輸送線般配非常不好時,將會萌生反射,只有一小批信號從發(fā)端傳道輸送到收繳設施,而其它局部將在送出端和收繳端之間往返反彈。在PCB上差分信號成功實現(xiàn)的好壞將對阻抗般配(以及其它方面)起非常大的效用。

差分走線預設

差分走線預設樹立在阻抗受控的PCB原理上。其板型有些像同軸電纜。在阻抗受控的PCB上,金屬最簡單的面層可以當作屏蔽層,絕緣體是FR4層壓板,而導體則是信號走線對(見圖1)。FR4的均勻介電常數(shù)在4.2到4.5之間。因為不曉得制作誤差,可能造成對銅線的過度腐刻,最后導致阻抗誤差。計算PCB走線阻抗的最非常準確辦法是利用途解析手續(xù)(一般是二維,有時用三維),它需求利用有限元對整個兒PCB批量直接解麥克斯韋方程。該軟件可以依據(jù)走線間距、線寬、線厚以及絕緣層的高度來剖析EMI效應。

100Ω特點標志阻抗已經(jīng)變成差分連署線的行業(yè)標準值。100Ω的差分線可以用兩根等長的50Ω單端線制造。因為兩根走線你我接近,線間的場耦合將減小線的差模阻抗。為了維持100Ω的阻抗,走線的寬度務必減小一點兒。最后結果,100Ω差分線對中每根線的共模阻抗將比50歐略為高一點兒。

理論上走線的尺寸和所用的材料表決了阻抗,但過孔、連署器乃至于部件焊盤都將在信號途徑中引入阻抗不蟬聯(lián)性。無須這些個物品一般是沒可能的。有時,為了更合理的布局和布線,就需求增加PCB的層數(shù),還是增加像埋孔這類功能。埋孔只連署PCB的局部層,不過在解決傳道輸送線問題的同時,也增加了扳手的制造成本。但有時根本沒有挑選。隨著信號速度越來越快,空間越來越小,像對埋孔這類的另外需要著手增加,這些個都應變成PCB解決方案的成本要素。

如圖2所示的橫剖面是實際差分線版圖的最常見圖案。在認為合適而使用帶狀線布線時,信號被FR-4材料夾在半中腰。而微帶線時,一條導體是顯露在空氣中的。由于空氣的介電常數(shù)最低(Er=1),故頂層最適應布設一點關鍵信號,如報時的鐘信號還是高頻的SERial-DESerial(SERDES)信號。微帶線布線應當耦合到下方的地最簡單的面,該地最簡單的面經(jīng)過借鑒局部電磁力場線來減小電磁干擾(EMI)。在帶狀線中,全部的電磁力場線耦合到上方和下方的參照最簡單的面,這大大減低了EMI。假如有可能的話,應當盡力不要用寬邊耦合帶狀線預設。這種結構容易遭受參照面中耦合的差分噪聲的影響。額外還需求PCB的平衡制作,這是很難扼制的。總的來說,扼制位于同一層上的線間距仍然比較容易的。

去耦和旁路容電器

另一個確認PCB的實際性能是否合乎預先期待的關緊方面需求經(jīng)過增加去耦和旁路電容施行扼制。增加去耦容電器有助于減小PCB的電源與地最簡單的面之間的電感,并有助于扼制PCB上到處的信號和IC的阻抗。旁路電容有助于為FPGA供給一個整潔的電源(供給一個電荷庫)。傳統(tǒng)規(guī)則是在便捷PCB布線的不論什么地方都應安置去耦電容,況且FPGA電源引腳的數(shù)目表決了去耦電容的數(shù)目。不過,F(xiàn)PGA的超高開關速度徹底突破了這種陳規(guī)。

在典型的FPGA板預設中,最接近電源的電容為負載的電流變動供給頻率償還。為了供給低頻濾波并避免電源電壓減退,要運用大的去耦電容。電壓減退是因為預設電路開始工作時穩(wěn)壓器的響應有所落后。這種大電容一般是低頻響應較好的電解電容,其頻率響應范圍從直流到幾百kHz。

每個FPGA輸出變動都要求對信號線充電和放電,這需求能+羭縷。旁路電容的功能是在寬頻率范圍內(nèi)供給部分能+羭縷儲存。額外,還需求串連電感細小的小電容來為高頻瞬變供給高速電流。而反響慢的大電容在高頻容電器能+羭縷耗費掉往后接著供給電流。

電源總線上數(shù)量多的電流瞬變增加了FPGA預設的復雜性。這種電流瞬變一般與SSO/SSN相關。插進去電感十分小的容電器將供給部分高頻能+羭縷,可用來消弭電源總線上的開關電流噪聲。這種避免高頻電流進入了部件電源的去耦電容務必十分接近FPGA(小于1cm)。有特殊情況將很多小電容并聯(lián)到一塊兒作為部件的部分能+羭縷儲存,并迅速響應電流的變動需要。

總的來說,去耦電容的布線應當完全的短,涵蓋過孔中的鉛直距離。即使是增加一點兒點也會增加導線的電感,因此減低去耦的效果。

其它技術

隨著信號速度的增長,要在電路板上輕松地傳道輸送數(shù)值變得一天比一天艱難。可以利用其它一點技術來進一步提高PCB的性能。

首先也是最表面化的辦法就是簡單的部件布局。為最關鍵的連署預設最短和最直接的途徑已經(jīng)是常識了,但不要過低估計了這一點兒。既是最簡單的策略可以獲得最好的效果,不必還要費勁去調(diào)試板上的信號呢?

幾乎一樣簡單扼要的辦法是要思索問題信號線的寬度。當數(shù)值率高達622MHz甚至于更高時,信號傳導的趨膚效應變受益發(fā)冒尖。當距離較長時,PCB上很細的走線(譬如4個或5個mil)將對信號形成非常大的衰減,就像一個沒有預設好的具備衰減的低通濾波器同樣,其衰減隨頻率增加而增加。背板越長,頻率越高,信號線的寬度應越寬。對于長度大于20英寸的背板走線,線寬應當達到10或12mil。

一般,扳手上最關鍵的信號是報時的鐘信號。當報時的鐘線預設得太長或非常不好的話,便會為下游放大抖動和偏移,特別是速度增加的時刻。應當防止運用多個層來傳道輸送報時的鐘,況且不要在報時的鐘線上有過孔,由于過孔將增加阻抗變動和反射。假如務必用內(nèi)層來布設報時的鐘,那末上下層應當運用地最簡單的面來減小延緩。當預設認為合適而使用FPGAPLL時,電源最簡單的面上的噪聲會增加PLL抖動。假如這一點兒很關鍵,可以為PLL開創(chuàng)一個“電源島”,這種島可以利用金屬最簡單的面中的較厚腐刻來成功實現(xiàn)PLL摹擬電源和數(shù)碼電源的隔離。

對于效率超過2Gbps的信號,務必思索問題成本更高的解決方案。在這樣高的頻率下,背板厚度和過孔預設對信號的完整性影響非常大。背板厚度不超過0.200英寸時效果較好。當PCB上為高速信號時,層數(shù)應盡有可能少,這么可以限止過孔的數(shù)目。在厚板中,連署信號層的過孔較長,將形成信號途徑上的傳道輸送線分支。認為合適而使用埋孔可以解決該問題,但制導致本頎長。另一種挑選是選用低消耗損失的介電材料,例如Rogers4350,GETEK或ARLON。這些個材料與FR4材料相形其成本有可能靠近翻倍,但有時候這是惟一的挑選。

還有其它一點用于FPGA的預設技術,他們可以供給I/O位置的一點挑選。在關鍵的高速SERDES預設中,可以經(jīng)過保存(但無須)相鄰的I/O引腳來隔離SERDESI/O。例如,相對于SERDESRx和Tx,VCCRX#和VCCTX#以及球位置,可以保存3x3或5x5BGA球地區(qū)范圍。還是假如有可能的話,可以保存接近SERDES的整個兒I/O組。假如預設中沒有I/O限止,這些個技術能夠帶來益處,并且不會增加成本。

最終,也是最好的辦法之一是參照FPGA制作商供給的參照板。絕大多制作商人團體供給參照板的源版圖信息,固然因為私人所有信息問題有可能需求特不要提出請求。這些個電路板一般里面含有標準的高速I/O接口,由于FPGA制作商在表征和證明它們的部件時需求用到這些個接口。然而要記取,這些個電路板一般是為多種用場預設的,不看出來與特別指定的預設需要剛好般配。固然這么,他們?nèi)钥梢宰鳛殚_創(chuàng)解決方案的起點。

本文小結

當然,本文只談及了一點基本的概念。這處所牽涉到的不論什么一個正題都可以用整本書的篇幅來商議。關鍵是要在為PCB版圖預設投入數(shù)量多時間和精神力之前搞明白目的是啥子。一朝完成了版圖預設,從新預設便會浪費數(shù)量多的時間和貨幣,即使是對走線的寬度作些微的調(diào)試。不可以倚賴PCB版圖工程師做出能夠滿意實際需要的預設來。原理圖預設師要一直供給引導,作出精明的挑選,并為解決方案的成功負起責任。

文章來自(www.4zj9t.cn)愛彼電路是專業(yè)高精密PCB電路板研發(fā)生產(chǎn)廠家,可批量生產(chǎn)4-46層pcb板,電路板,線路板,高頻板,高速板,HDI板,pcb線路板,高頻高速板,IC封裝載板,半導體測試板,多層線路板,hdi電路板,混壓電路板,高頻電路板,軟硬結合板等